publications

publications by categories in reversed chronological order. generated by jekyll-scholar.

2025

-

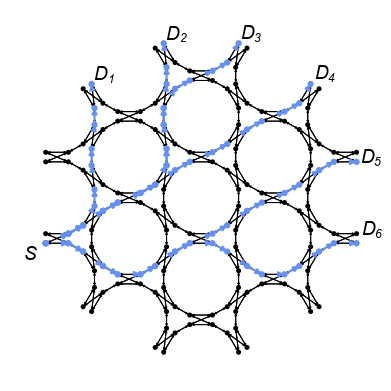

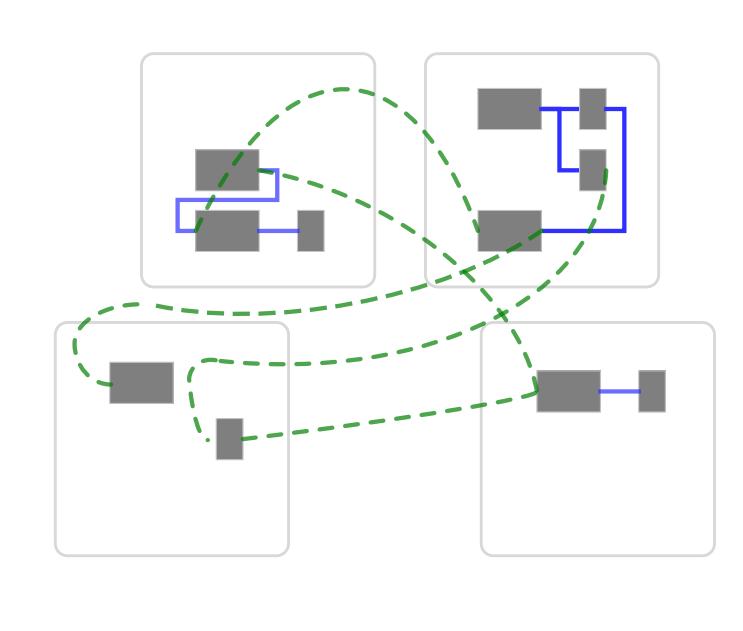

Dense or Sparse? Post-Packing Interconnection Analysis in FPGAsIn Proceedings of the International Symposium on Highly Efficient Accelerators and Reconfigurable Technologies (HEART 2025), 2025

Dense or Sparse? Post-Packing Interconnection Analysis in FPGAsIn Proceedings of the International Symposium on Highly Efficient Accelerators and Reconfigurable Technologies (HEART 2025), 2025 -

Adaptive elite learning particle swarm optimization algorithm with complementary sub-strategies for multimodal problemsSCIENCE CHINA Information Sciences, 2025Available online: Jul 3, 2025

Adaptive elite learning particle swarm optimization algorithm with complementary sub-strategies for multimodal problemsSCIENCE CHINA Information Sciences, 2025Available online: Jul 3, 2025 -