Xiaoke Wang 王筱轲

I am presently pursuing my Ph.D. studies within the UGent Hardware Embedded System (HES) team at the CSL lab, under the guidance of Prof. Dirk Stroobandt since Oct. 2023. I obtained my MSc in Electrical Engineering from Ghent University in 2023.

My current research focuses on interconnect-aware EDA (logic synthesis and physical design) — especially optimizing netlist interconnect structure to accelerate FPGA physical design and resolve interconnect bottlenecks in 2.5D/3D FPGA systems. I am open to research collaboration in related topics. Let me know if you are interested!

News

| Mar 06, 2026 | Started serving as a reviewer for Swarm and Evolutionary Computation. |

|---|---|

| Mar 01, 2026 | Serving as Web Chair for FPL 2026, which will be held in Ghent. Welcome to submit your work. |

| Feb 25, 2026 | Our journal article on DPU benchmarking was accepted by Integration, the VLSI Journal. |

| Oct 16, 2025 | Won the Bronze Award in the TechArena Ph.D. Student Contest 2025 (Silicon Photonics). |

| Oct 11, 2025 | Our conference paper was accepted and presented at FPT 2025. |

| Sep 13, 2025 | Our work on logic resynthesis was presented at SLIP 2025. |

| Jun 11, 2025 | Our journal article on particle swarm optimization was accepted by SCIENCE CHINA Information Sciences (SCIS). |

| Mar 11, 2025 | Our conference paper on FPGA packing was accepted and presented at HEART 2025. |

| Nov 28, 2024 | My Ph.D. poster was presented at FEARs 2024. |

| Nov 19, 2024 | Our journal article was accepted by IEEE/Optica Journal of Lightwave Technology (JLT). |

| Oct 31, 2024 | Our workshop paper titled “The Influence of Interconnection Complexity on the FPGA CAD Flow” was presented at SLIP 2024. |

Publications

2026

2025

-

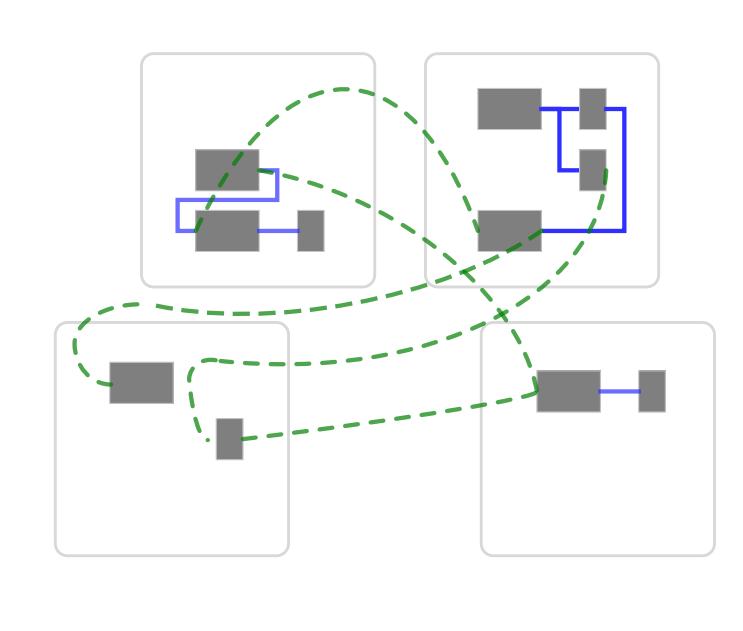

Dense or Sparse? Post-Packing Interconnection Analysis in FPGAsIn Proceedings of the International Symposium on Highly Efficient Accelerators and Reconfigurable Technologies (HEART 2025), 2025

Dense or Sparse? Post-Packing Interconnection Analysis in FPGAsIn Proceedings of the International Symposium on Highly Efficient Accelerators and Reconfigurable Technologies (HEART 2025), 2025 -

Adaptive Elite Learning Particle Swarm Optimization Algorithm with Complementary Sub-Strategies for Multimodal ProblemsSCIENCE CHINA Information Sciences, 2025Available online: Jul 3, 2025

Adaptive Elite Learning Particle Swarm Optimization Algorithm with Complementary Sub-Strategies for Multimodal ProblemsSCIENCE CHINA Information Sciences, 2025Available online: Jul 3, 2025 -

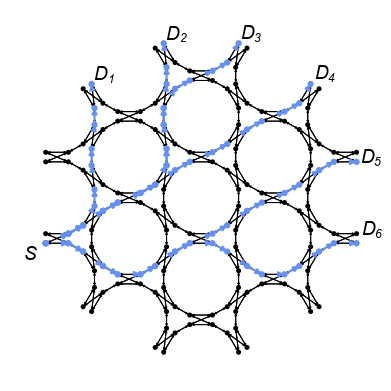

Length-Matching Routing for Programmable Photonic Circuits Using Best-First StrategyIn 2025 International Conference on Field Programmable Technology (ICFPT), 2025

Length-Matching Routing for Programmable Photonic Circuits Using Best-First StrategyIn 2025 International Conference on Field Programmable Technology (ICFPT), 2025 -

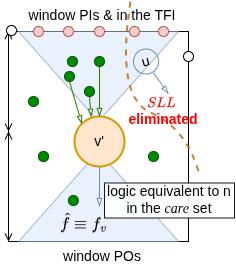

Interconnection-Aware Resynthesis for Improving FPGA Physical DesignIn 2025 35th International Conference on Field-Programmable Logic and Applications (FPL), 2025